- 您现在的位置:买卖IC网 > Sheet目录3828 > ATMEGA169P-16MCU (Atmel)MCU AVR 16K ISP FLSH 16MHZ 64QFN

2005 Microchip Technology Inc.

Preliminary

DS41265A-page 177

PIC16F946

14.12.2

RECEPTION

When the R/W bit of the address byte is clear and an

address match occurs, the R/W bit of the SSPSTAT

register is cleared. The received address is loaded into

the SSPBUF register.

When the address byte overflow condition exists, then

no Acknowledge (ACK) pulse is given. An overflow

condition is defined as either bit BF (SSPSTAT<0>) is

set, or bit SSPOV (SSPCON<6>) is set. This is an error

condition due to the user’s firmware.

An SSP interrupt is generated for each data transfer

byte. Flag bit SSPIF (PIR1<3>) must be cleared in

software. The SSPSTAT register is used to determine

the status of the byte.

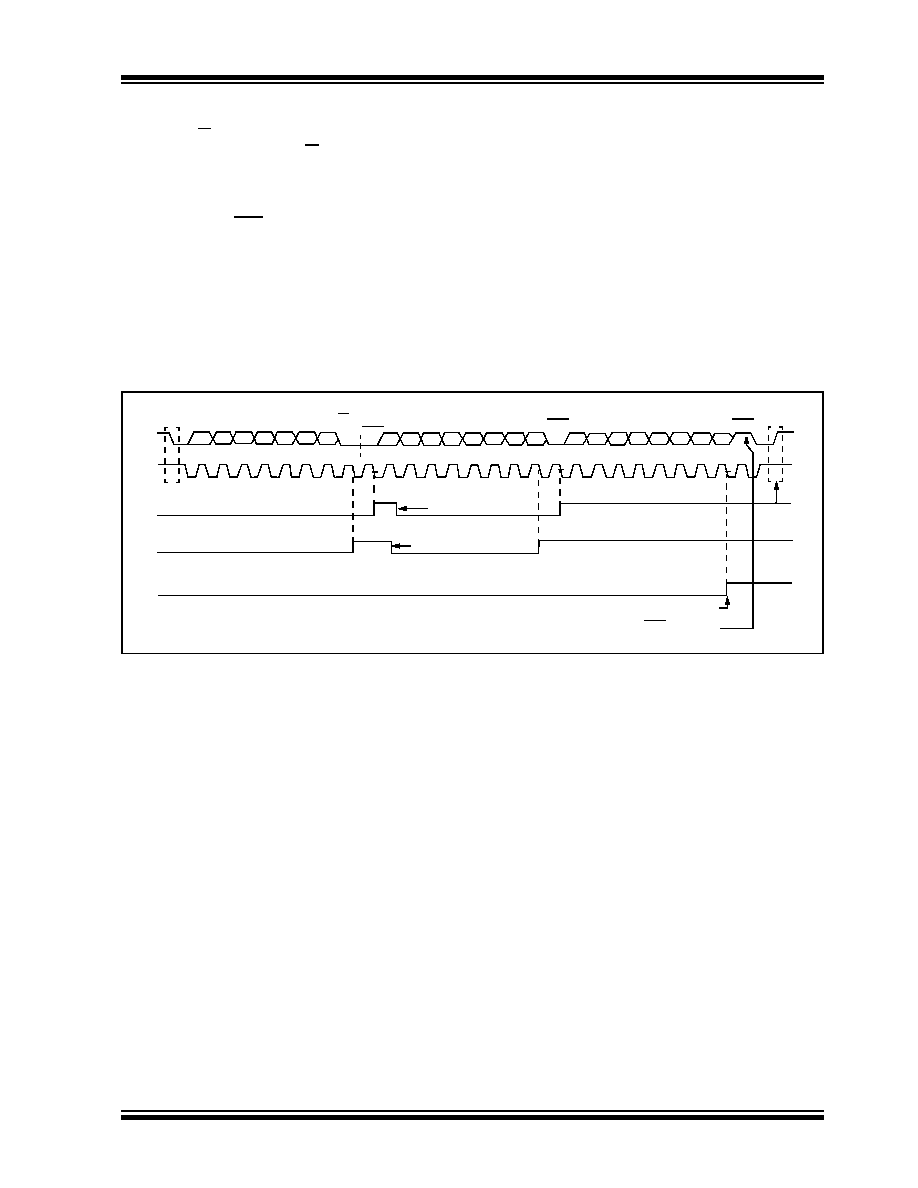

FIGURE 14-8:

I2C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

P

9

8

7

6

5

D0

D1

D2

D3

D4

D5

D6

D7

S

A7 A6 A5 A4 A3 A2 A1

SDA

SCL

12

3

4

5

6

7

8

9

12

3

4

56

7

89

12

3

4

Bus Master

terminates

transfer

Bit SSPOV is set because the SSPBUF register is still full.

Cleared in software

SSPBUF register is read

ACK

Receiving Data

D0

D1

D2

D3

D4

D5

D6

D7

ACK

R/W = 0

Receiving Address

SSPIF (PIR1<3>)

BF (SSPSTAT<0>)

SSPOV (SSPCON<6>)

ACK

ACK is not sent.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT91SAM7XC256-CU

MCU ARM 256K HS FLASH 100-TFBGA

PIC16LF874A-I/P

IC MCU FLASH 4KX14 EE A/D 40DIP

PIC16F84-10/SO

IC MCU FLASH 1KX14 EE 18SOIC

AT91SAM7XC128-CU

MCU ARM 128K HS FLASH 100-TFBGA

PIC18F2458-I/SO

IC PIC MCU FLASH 12KX16 28SOIC

PIC18F4455-I/P

IC PIC MCU FLASH 12KX16 40DIP

AT91SAM7X256-CU

MCU ARM 256K HS FLASH 100-TFBGA

PIC16C73B-20/SS

IC MCU OTP 4KX14 A/D PWM 28SSOP

相关代理商/技术参数

ATMEGA169P-16MU

功能描述:8位微控制器 -MCU AVR 16K FLASH 512B EE 1K SRAM LCD ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU SL383

制造商:Atmel Corporation 功能描述:MCU 8BIT ATMEGA RISC 16KB FLASH 3.3V/5V 64PIN MLF - Tape and Reel

ATMEGA169P-16MUR

功能描述:8位微控制器 -MCU AVR LCD 16KB FLSH EE 512B 1KB SRAM-16MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-8AU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169P-8MU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA_1

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Endurance Non-volatile Memory segments

ATMEGA169PA-AN

功能描述:8位微控制器 -MCU AVR XMEGA 384KB 105C 4KB EE32K SRAM-16MHz RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT